# Time Delay Considerations in High-Frequency Phase-Locked Loops

James Buckwalter and Robert A. York

University of California- Santa Barbara, Santa Barbara, CA, 93106

**Abstract** — The time-delayed phase-locked loop (PLL) model predicts drastically different behavior not accounted for in a conventional PLL model. Three results in particular are identified. A critical gain exists for which the equilibrium point becomes a limit cycle. An optimal gain exists that minimizes the acquisition time of the PLL to an external signal. Finally, changes in stability occur first at zero frequency detuning for a given gain and time delay. Verification of this behavior in a 1.5 GHz PLL with reasonable circuit parameter values is demonstrated.

## I. INTRODUCTION

Extensive analysis of phase-locked loop (PLL) dynamics has been provided in texts and the research literature [1]. Our motivation is to highlight fundamentally different dynamical behavior in a PLL due to loop time delay than is typically presented. The analysis of the PLL is based on circuit parameters such gain, time delay, filter response, and frequency detuning. The filter is assumed low-pass. Other authors have demonstrated the circuit instability regions that result from a time delayed PLL model [2]. Our intention is to limit the analysis to the conditions that result in changes to the stability of a high frequency PLL.

Several PLL circuits were designed that displayed strong spurious harmonics not related to oscillations resulting from gain and phase margin instability. Instead, insight into these oscillations led to an examination of time-delay as an oscillation-inducing circuit parameter.

First, we examine a conventional PLL model. Developing a method to approaching the non-linear behavior of the conventional PLL model is helpful when time delay is introduced into the model.

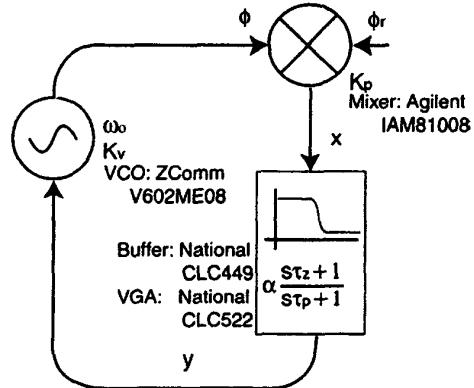

Fig.1 suggests the follow system of equations.

$$\begin{aligned} \tau_p \dot{y} + y &= \alpha(\tau_z \dot{x} + x) \\ x &= K_p \sin(\phi) \sin(\phi_r) \\ \dot{\phi} &= \omega_0 + K_v y \end{aligned} \quad (1)$$

The voltage-controlled oscillator (VCO) is characterized with a natural frequency  $\omega_0$  and a tuning sensitivity  $K_v$ . The phase output,  $\phi$ , represents the argument of a periodic function. The mixer multiplies two periodic signals with gain of  $K_p$  producing an error

signal. This signal is low-pass filtered with pole and zero time constants,  $\tau_p$  and  $\tau_z$ , and amplification,  $\alpha$ .

Fig. 1. PLL topology

Substituting for each equation and subtracting a reference signal with constant phase results in the following second-order differential equation.

$$\begin{aligned} \tau_p \Delta \ddot{\phi} + (1 + \tau_z G \sin \Delta \phi) \Delta \dot{\phi} - G \cos \Delta \phi &= \Delta \omega \\ \text{where } G &= \frac{1}{2} \alpha K_p K_v, \Delta \phi = \phi - \phi_r, \text{ and } \Delta \omega = \omega_0 - \omega_r \end{aligned} \quad (2)$$

We will refer to  $G$  as the open-loop gain,  $\Delta \phi$  as the phase difference, and  $\Delta \omega$  as the frequency detuning. Note that  $G$  has units of MHz.

(2) can be cast as

$$\begin{aligned} \dot{\bar{x}} &= f(\bar{x}), \bar{x} = \begin{bmatrix} \Delta \phi \\ \Delta \dot{\phi} \end{bmatrix} \rightarrow \\ \dot{x}_1 &= x_2 \\ \tau_p \dot{x}_2 &= -(1 + \tau_z G \sin x_1) x_2 + G \cos x_1 + \Delta \omega \end{aligned} \quad (3)$$

The behavior of interest occurs near the equilibrium points. These points are defined as satisfying  $f(\bar{x}) = 0$ . Solving (3) gives an equilibrium point at

$$\bar{x}_{eq} = \begin{bmatrix} \cos^{-1} \left( \frac{-\Delta \omega}{G} \right) \\ 0 \end{bmatrix}. \quad (4)$$

Consequently, equilibrium points exist only where the inverse cosine exists. This implies that the hold-in range, the range of detuning that remains in phase lock, is  $2G$ . Calculating the open-loop gain from a measurement of the hold-in range does not require breaking the feedback loop and is often practical for studying loop behavior.

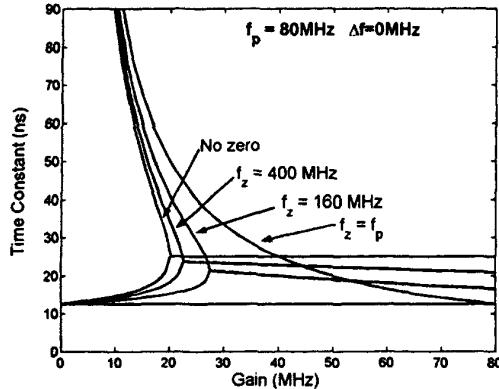

Studying the stability of the PLL is reduced to studying the eigenvalues of (3) near the equilibrium points. These eigenvalues determine the time constants of the response of the PLL toward an equilibrium point. Fig. 2 relates the time constants (via the eigenvalues) versus gain for several filter zero values.

Fig. 2. Time constant versus gain for several filter zero values.

A few features are notable. First, the time constant is positive for all values of  $G$  and consequently all equilibrium points are absolutely stable. This will not be true in the time-delay situation.

Second, the graphs bifurcate below an optimal gain value. The coalescence of the time constants above this optimal gain minimizes the acquisition time. The filter zero allows the time constant to decrease beyond the bifurcating time constant value and, hence, the acquisition time improves with gain. Without a filter zero, increasing gain does not improve acquisition time. Given a particular gain, the fastest acquisition occurs at a zero value for which the eigenvalues bifurcates at smaller gains.

## II. TIME DELAY PLL MODEL

The PLL model can be modified to incorporate a lump sum time delay between the mixer and the VCO. (2) becomes

$$\begin{aligned} \tau_p \Delta \ddot{\phi} + \Delta \dot{\phi} + \tau_z G \Delta \dot{\phi} (t - T) \sin \Delta \phi (t - T) \\ - G \cos \Delta \phi (t - T) = \Delta \omega \end{aligned} \quad (5)$$

We want to express this as a system of equations as we did in (3). This motivates introducing

$$x_3(t) = x_1(t - T) \quad x_4(t) = x_2(t - T) \quad (6)$$

Since true time delay is an infinite dimensional variable, analyzing the exact equation is a challenge. One approach is to approximate the Laplace transform of the time-delayed signal. The Pade approximation allows us to express the time delay as a transfer function [3]. The first order Pade (1,1) approximation is

$$\frac{X_3(s)}{X_1(s)} = e^{-sT} \approx \frac{1 - \frac{1}{2}sT}{1 + \frac{1}{2}sT} \quad (7)$$

Using this relationship, the system of equations becomes four-dimensional.

$$\begin{aligned} \dot{x}_1 &= x_2 \\ \tau_p \dot{x}_2 &= -x_2 - \tau_z G x_4 \sin x_3 + G \cos x_3 + \Delta \omega \\ \dot{x}_3 &= \frac{2}{T} (x_1 - x_3) - x_2 = x_4 \\ \tau_p \dot{x}_4 &= \frac{2\tau_p}{T} (x_2 - x_4) + x_2 + \tau_z G x_4 \sin x_3 - G \cos x_3 - \Delta \omega \end{aligned} \quad (8)$$

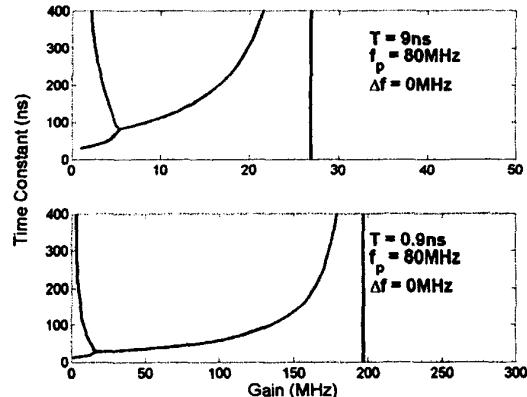

Two values of time delay are presented in Fig. 3. The stability of the equilibrium point is qualitatively similar for all zero frequencies. To simplify analysis, we assume there is no zero. Comparing Fig. 2 and Fig. 3, the most important features of the two time delay graphs are the singularity and the non-monotonic behavior of the time constant values.

Fig. 3. Time constant versus gain comparison for two time delays.

The singularity changes the stability of the equilibrium point. Once the real part of any of the eigenvalues becomes positive and, consequently, the time constant becomes negative, the PLL will no longer lock at an equilibrium point. The PLL locks instead in a limit cycle to the injected signal.

The relationship between gain and time delay is implicit in comparing these plots; a factor of ten increase in the time delay results in roughly a factor of ten decrease in the zero crossing or critical gain.

Furthermore, the acquisition time of the PLL is minimized at a particular gain for a given delay. The optimal gain for fast acquisition is the gain that minimizes the time constants. As seen in Fig. 3, this occurs for gains of 5 and 10 MHz, respectively. Surprisingly, the large change in time delay has little impact on this optimal gain. From Fig. 2, the conventional PLL gives an upper bound on the optimal gain at 20 MHz. Comparing Fig. 2 and Fig. 3 demonstrates the similar time constant behavior for gains below the optimal gain.

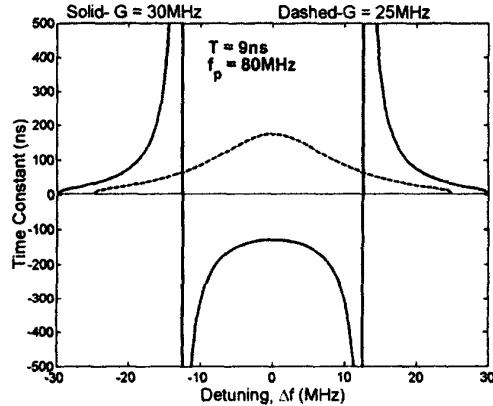

Fig. 4. Time constant versus frequency detuning comparison for two gains.

Variation of frequency detuning results in a stable equilibrium point for some values of detuning and limit cycle for other values. Fig. 4 demonstrates the behavior under these circumstances. First, for gains greater than the critical gain illustrated in Fig. 3, some region of detuning results in a limit cycle, as reflected by the negative time constant value. Second, for zero frequency detuning (the oscillators have the same natural frequencies) the time constant is largest.

Three unique behaviors have been identified: 1) the critical gain, 2) the optimal gain, and 3) zero detuning instability. We have verified these three behaviors in a 1.5 GHz PLL.

### III. MEASUREMENT AND VERIFICATION OF PLL BEHAVIOR

The circuit consists of a mixer, buffer, variable gain amplifier (VGA), and a VCO as in Fig. 1. The VGA provides gain and natural frequency control, allowing variation of  $G$  and  $\Delta\omega$ . The time delay results from the intrinsic transit and charging times of the devices and the layout topology. The loop was broken and the step signal was applied to measure the time delay. While the delay was expected to be about 7 nanoseconds, the measurement was 9.0 nanoseconds. The filter pole is at 80 MHz. There is no filter zero. These values are used in the predictions of the previous section to facilitate direct comparison.

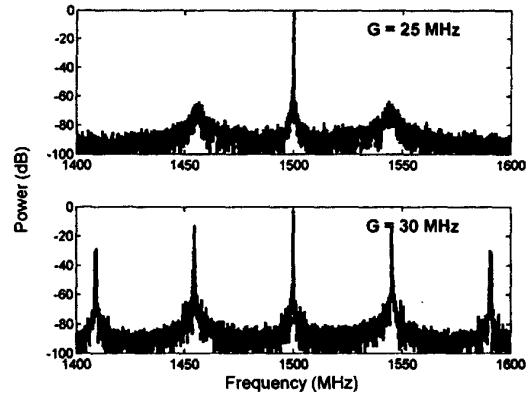

#### A. Critical Gain Behavior

According to Fig. 3, at the critical gain the time constant changes sign. For higher gain, the loop still locks but the equilibrium point becomes a limit cycle.

Fig. 5. Critical gain region frequency spectrum.

Verifying the critical gain consists of determining the boundary between an absolutely stable locked state and a locked state that displays a limit cycle. The frequency spectrum of the VCO signal in Fig. 5 is the best indicator of the bifurcation boundary. The spectrum demonstrates the sidelobes resulting from the limit cycle behavior of the equilibrium point. In the top spectrum, the spurious harmonics are 60dB below the oscillator frequency. A slight increase in gain results in harmonic components of power on the order of the carrier as shown on the bottom. The pull-in range is measured to estimate the gain. Comparing with Fig. 3, the critical gain is between 25 and 30 MHz as predicted.

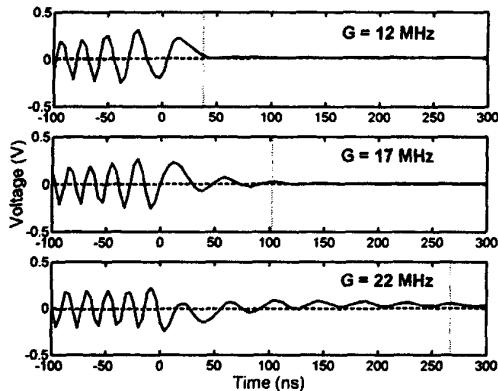

#### B. Optimal Gain Behavior

Time delay degrades the acquisition time of the PLL with increasing gain. This result contradicts the conventional model, which predicts gain will monotonically improve acquisition time. Three time domain responses demonstrate this degradation in Fig. 6.

These measurements should be considered for qualitative value since the initial conditions cannot be closely controlled. An external pulse forces the PLL out of lock initially. This condition results in the beat note response prior to the active low pulse in Fig. 6. After the pulse is turned off, the system proceeds to lock.

Though the actual acquisition times differ from the expected values in Fig. 3., the qualitative agreement is more compelling than for the conventional model.

Fig. 6. Acquisition times for increasing gain.

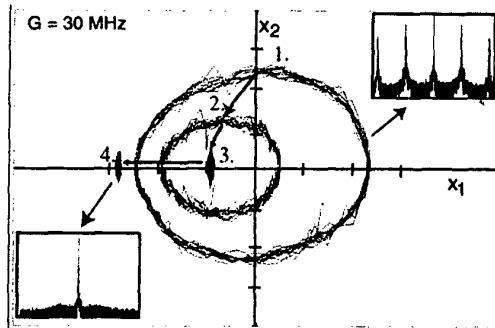

#### C. Frequency Detuning Instability

Fig. 4. illustrates changes in the stability of the system with frequency detuning. To compare the circuit behavior with the theoretical behavior for frequency detuning, the phase plane is measured. Fig. 7 consists of four measurements of the phase plane for different detuning values. The axes correspond to the  $x$  variables of (8). The largest limit cycle occurs for zero frequency detuning. The arrows leading from 1 through 4 imply the continuity of the limit cycle as it collapses to an equilibrium point for maximal frequency detuning. Additionally the frequency spectra for 1 and 4 are presented to relate the phase plane behavior to a spectrum analyzer. The detuning variation is symmetric as is expected from Fig 4.

Finally, note that the actual collapse of the limit cycle occurs between 7 and 10 MHz. Fig. 4. predicts this collapse at 12 MHz.

Fig. 7. Stability variations with frequency detuning. 1) corresponds to 0 MHz detuning. 2) corresponds to 7 MHz detuning. 3) corresponds to 10 MHz detuning. 4) corresponds to 29 MHz detuning.

#### IV. CONCLUSION

Inclusion of time delay in a PLL model predicts instability unaccounted for in the conventional model. Several important results of the bifurcating dynamics have been identified. A critical gain exists above which the oscillators will no longer lock with a time-independent phase difference. An optimal gain exists that provides the fastest possible acquisition time for the two oscillators. Finally, a variation exists in the stability of an equilibrium point with respect to frequency detuning. These dynamics have been studied in a 1.5 GHz phase locked loop and have been determined to closely agree to the first order predicted behavior.

#### ACKNOWLEDGEMENT

The authors wish to acknowledge ONR support through grant #N0014-00-1-0015. We appreciate the support and encouragement of Brian Meadows at SPAWAR.

#### REFERENCES

- [1] H. Meyr and G. Ascheid, *Synchronization in Digital Communications*, New York: John Wiley & Sons, 1990.

- [2] W. Wischert, M. Olivier, and J. Groslambert, "Frequency Instabilities in Phase-Locked Synthesizers Induced by Time Delay," *Proceedings of the 1992 IEEE Frequency Control Symposium*, pp. 201-6, May 1992.

- [3] G. F. Franklin, J.D. Powell, and A. Emami-Naeini, *Feedback Control of Dynamic Systems*, 3 rd ed., MA: Addison-Wesley, 1994.